集成电路(IC)设计是现代电子技术的核心,涵盖了从概念到实际芯片实现的多个阶段。其中,物理设计作为关键环节,直接决定了芯片的性能、功耗、面积和可靠性。本文将从物理设计的基本概念、主要流程、技术挑战以及未来发展趋势等方面进行探讨。

一、物理设计的基本概念

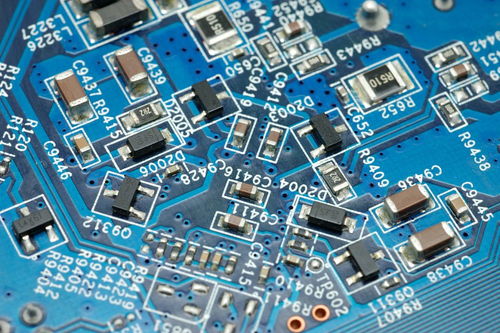

物理设计是指将逻辑电路转换为实际的物理布局的过程,涉及晶体管、互连线和其他元件的几何排列。这一阶段的目标是在满足时序、功耗和面积约束的前提下,实现电路功能的高效映射。物理设计不仅需要考虑电路的正确性,还必须应对制造工艺的限制,如光刻精度、寄生效应和热管理等问题。

二、物理设计的主要流程

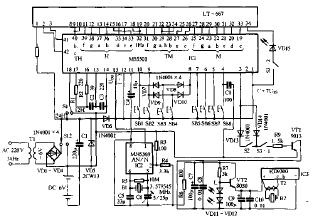

物理设计通常包括以下几个关键步骤:

- 布局规划:确定芯片上各个功能模块的位置和形状,优化整体面积和互连长度。

- 单元布局:将逻辑单元(如门电路、存储器)放置在芯片的特定位置,确保时序和功耗要求。

- 时钟树综合:设计时钟分布网络,以减少时钟偏差和抖动,保证同步电路的稳定性。

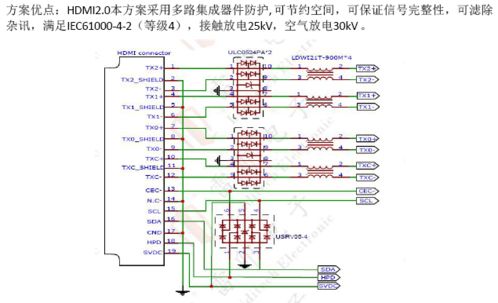

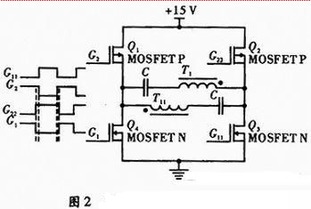

- 布线:连接各个单元和模块,形成互连网络。布线过程需考虑信号完整性、串扰和延迟问题。

- 物理验证:通过设计规则检查(DRC)、布局与电路图一致性检查(LVS)等工具,确保设计符合制造规范。

三、物理设计的技术挑战

随着集成电路工艺节点的不断缩小,物理设计面临诸多挑战:

- 寄生效应:互连线的电阻、电容和电感效应会显著影响信号延迟和功耗,需通过精确建模和优化来缓解。

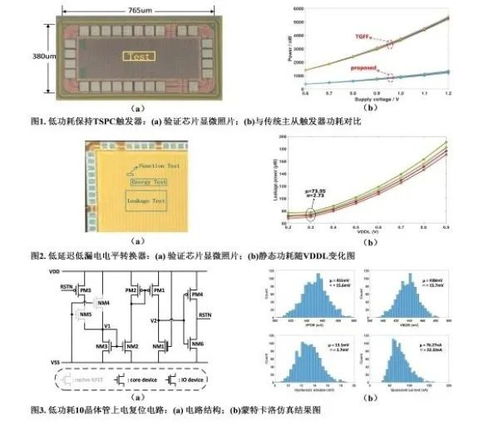

- 功耗管理:在高性能芯片中,动态和静态功耗的控制至关重要,物理设计需采用低功耗技术,如电源门控和多电压域设计。

- 制造变异:纳米级工艺中的工艺变异可能导致性能偏差,物理设计需引入统计方法和冗余设计以提高良率。

- 热效应:高密度集成易导致局部过热,物理设计需通过热分析和散热设计来确保芯片可靠性。

四、未来发展趋势

物理设计正朝着自动化、智能化和多物理场协同优化的方向发展:

- AI辅助设计:机器学习和人工智能技术被广泛应用于布局和布线优化,提升设计效率和质量。

- 3D集成:通过堆叠芯片技术,物理设计需解决热管理和互连复杂性等问题,以实现更高性能。

- 新兴材料与工艺:碳纳米管、二维材料等新技术的引入,将推动物理设计方法的革新。

物理设计是集成电路设计中不可或缺的一环,它不仅决定了芯片的最终性能,还直接影响到制造成本和上市时间。随着技术的进步,物理设计将继续演进,为更复杂、高效的集成电路提供支持。