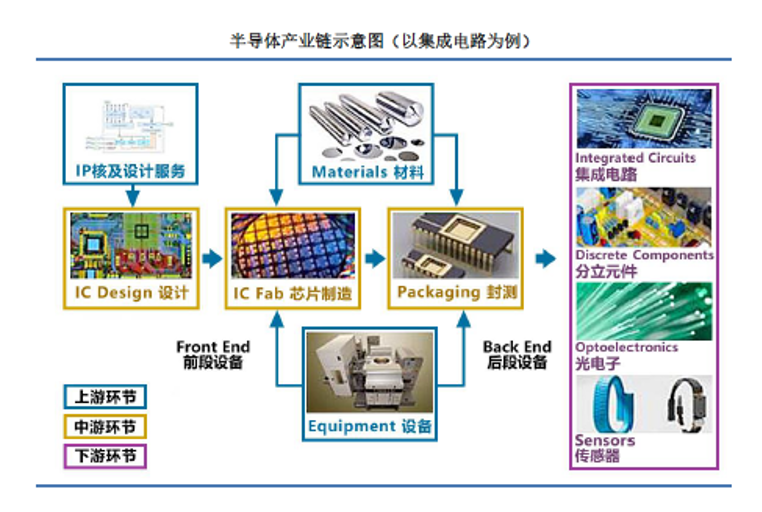

随着集成电路设计复杂度的不断提升,模拟电路尤其是多级串联结构(如多级放大器、滤波器、电压基准源等)的设计与测试面临着严峻挑战。传统的测试方法往往依赖外部探针与功能验证,不仅效率低下,且难以深入定位内部故障。因此,可测性设计技术已成为确保模拟电路可靠性、降低测试成本、提高产品良率的关键环节。本文将系统分析多级串联模拟电路的可测性设计技术,探讨其在现代集成电路设计中的应用与优化策略。

一、多级串联模拟电路的测试挑战

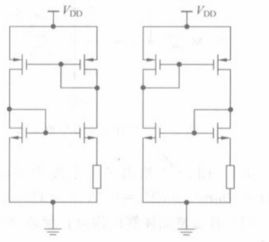

多级串联模拟电路通常由多个功能级联构成,信号在各级间连续传递与处理。这种结构带来了独特的测试难题:内部节点难以直接观测,故障隔离困难;各级间存在复杂的耦合与负载效应,单一故障可能引发级联错误,导致故障混淆;模拟信号的连续性与高精度要求使得数字电路中常用的扫描链、内建自测试等方法难以直接适用。因此,需要专门的可测性设计技术来增强电路的可控性与可观测性。

二、核心可测性设计技术

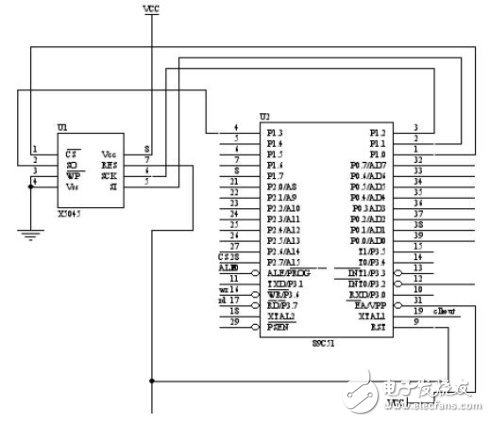

- 测试点插入技术:通过在关键内部节点(如级间连接点、偏置电路节点)插入可控测试点,允许外部测试设备或片上电路注入测试信号或观测响应。例如,采用模拟多路复用器将内部节点切换到测试引脚,或引入可切换的测试激励源。这有助于隔离故障级,提高测试覆盖率。

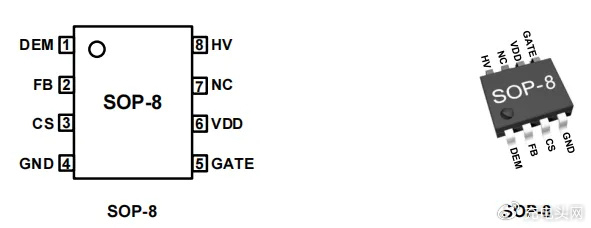

- 基于DfT的模块化设计:将多级电路划分为相对独立的模块(如单级放大器、滤波节),并为每个模块设计专用测试接口。通过内建测试电路(如片上传感器、比较器)实现模块级功能验证,减少对外部测试仪的依赖。模块化设计还能支持并行测试,缩短测试时间。

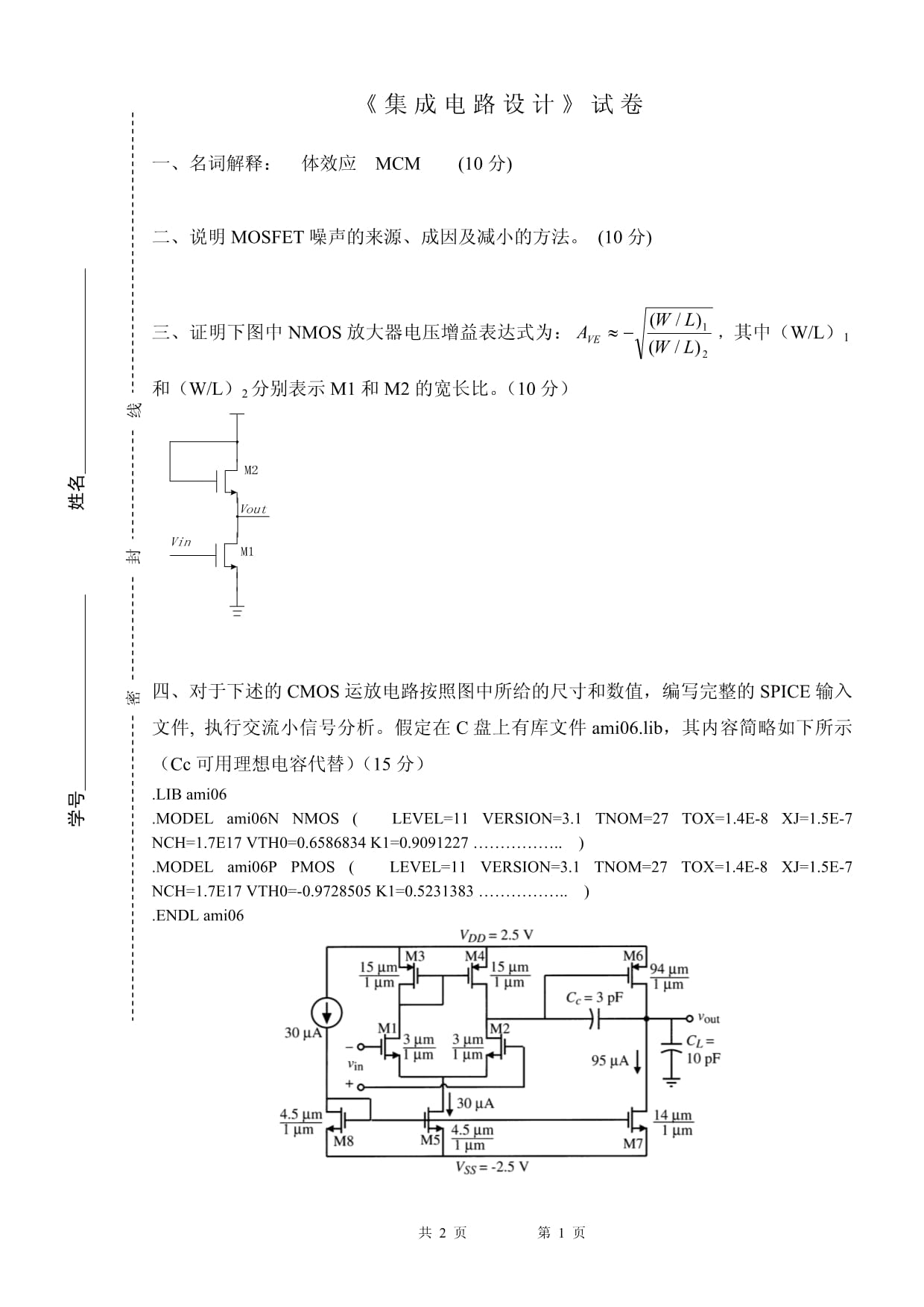

- 故障建模与仿真:针对模拟电路常见的故障类型(如参数漂移、开路/短路),建立精确的故障模型。利用仿真工具(如SPICE)分析故障传播路径,优化测试激励设计。例如,设计特定频率或幅度的测试信号,以放大故障效应,提高测试灵敏度。

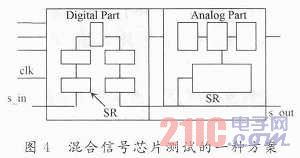

- 混合信号DfT技术:结合数字与模拟可测性设计优势,例如在模拟电路周边集成数字控制逻辑,实现测试模式切换、数据采集与处理。采用Σ-Δ调制器等技术将模拟信号转换为数字位流,再利用数字BIST进行高效分析。

三、技术集成与优化策略

在实际集成电路设计中,可测性技术需与性能、面积、功耗等指标权衡。优化策略包括:

- 分级测试策略:根据电路关键性分配测试资源,对敏感级(如输入级、输出级)实施高精度测试,对非关键级采用简化测试。

- 自适应测试技术:利用片上监控电路实时监测参数变化,动态调整测试方案,适应工艺波动与环境因素。

- 标准化接口:遵循IEEE 1149.4等混合信号测试标准,设计统一测试总线,提升测试兼容性与自动化水平。

四、未来发展趋势

随着物联网、汽车电子等应用对模拟电路可靠性要求日益提高,可测性设计技术正朝向智能化、集成化发展。机器学习方法被用于优化测试模式生成;先进封装技术(如2.5D/3D集成)推动着跨层级测试方案创新;基于仿生原理的自我修复电路也为可测性设计提供了新思路。

多级串联模拟电路的可测性设计是一项多学科交叉的复杂工程,需要从电路架构、测试算法到芯片实现的全流程协同。通过深度融合DfT理念,不仅能提升测试效率,更能增强电路在复杂环境中的稳健性,为高性能集成电路的可持续发展奠定基础。