自偏置电路(Self-Biasing Circuits)是现代模拟射频集成电路(Analog RF IC)设计中不可或缺的核心技术之一。其核心价值在于通过电路自身的反馈机制,自动建立并稳定晶体管的工作点(如偏置电流和电压),从而显著降低对外部精密偏置电压源的依赖,并有效提升电路对工艺偏差、温度变化和电源波动的鲁棒性。在EETop等国内外最大最火的半导体、集成电路设计社区中,自偏置电路的设计与优化始终是工程师们热烈讨论的焦点话题,它紧密连接着模拟IC、射频IC、嵌入式系统及更广泛的电子电路设计领域。

一、自偏置电路的基本原理与优势

在模拟射频IC中,放大器、振荡器、混频器等核心模块的晶体管必须工作在合适的静态工作点(Q点),以确保增益、线性度、噪声系数和频率响应等关键性能指标。传统的外加固定偏置电压方法,容易受到片上电阻与晶体管阈值电压的工艺偏差影响,导致批次间性能离散,且在温度变化时工作点漂移严重。

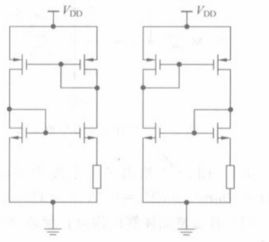

自偏置电路巧妙地利用电流镜、带隙基准(Bandgap Reference)原理或负反馈环路,生成一个与电源电压和工艺参数(如载流子迁移率)相关性较低的基准电流或电压。例如,一个经典的共源共栅(Cascode)电流镜结合一个启动电路,可以构成一个稳定的偏置核心。其核心优势在于:

- 提高工艺容差:通过使偏置电流与电阻的绝对值解耦(例如,利用ΔVgs/R的结构,使电流正比于迁移率但反比于迁移率,从而部分抵消工艺影响),减小芯片之间的性能差异。

- 增强温度稳定性:通过引入正温度系数与负温度系数元件(如双极型晶体管BJT与电阻)的组合,实现接近零温度系数的基准,稳定跨导(gm)等关键参数。

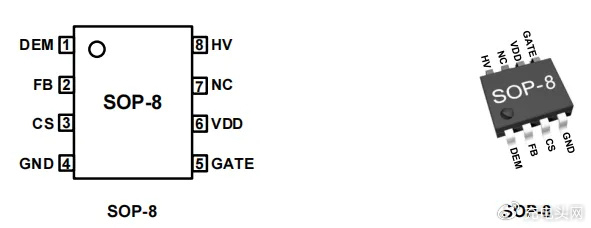

- 简化系统设计:减少外部引脚和片外元件,有利于实现更高集成度的SoC(片上系统)和嵌入式设计。

- 改善电源抑制比(PSRR):良好的自偏置设计能有效抑制电源纹波对内部工作点的干扰,这对噪声敏感的高频射频电路至关重要。

二、模拟射频IC设计中的自偏置实现

在射频领域,自偏置设计面临更严峻的挑战,因为工作频率往往高达GHz级别,寄生电容、电感效应显著,且需要兼顾噪声、线性度和功耗。

- 低噪声放大器(LNA)的偏置:LNA的偏置点直接影响其噪声系数(NF)和增益。常采用电流复用技术或自偏置的共源结构,在提供合适静态电流的确保输入阻抗匹配,并避免偏置电阻引入的额外热噪声。

- 功率放大器(PA)的偏置:对于AB类或Doherty PA,其偏置点设定对效率和线性度权衡至关重要。自适应偏置或自偏置技术可用于补偿晶体管阈值电压随温度和高功率输出下的变化(自热效应),防止性能退化。

- 压控振荡器(VCO)的偏置:VCO核心的交叉耦合对管需要精确的电流偏置以控制振荡幅度和相位噪声。采用自偏置尾电流源可以抑制电源噪声上变频,改善相位噪声性能。

- 混频器与频率合成器:吉尔伯特单元(Gilbert Cell)等有源混频器的开关对管和跨导管也需要稳定的偏置,以保持转换增益和线性度。

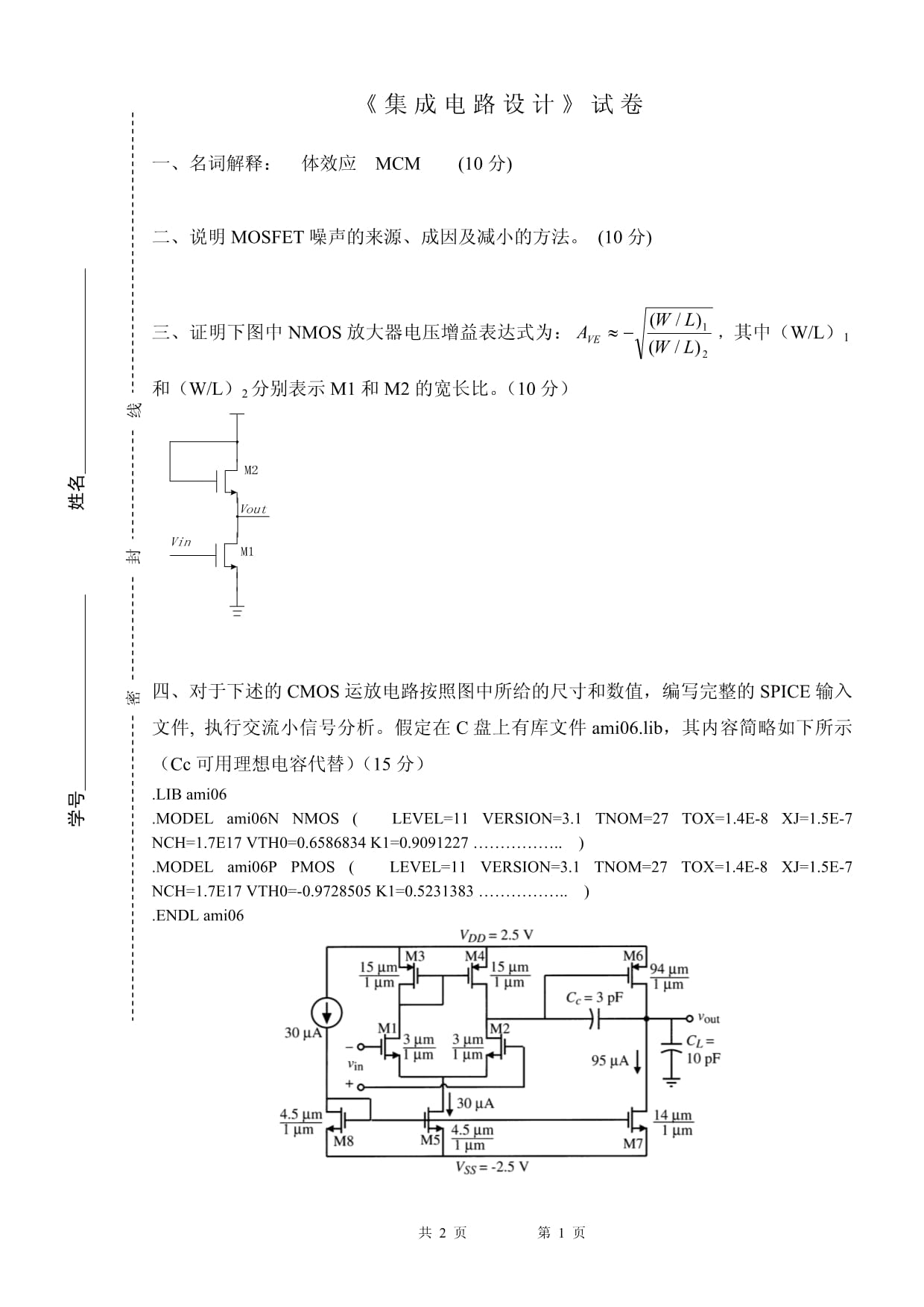

设计时需利用先进的仿真工具(如Cadence Virtuoso, ADS),进行直流、交流、瞬态、噪声以及最坏情况(Monte Carlo, Corner)仿真,以验证自偏置电路在各种工艺角和温度下的稳定性。

三、社区讨论与设计资源

在EETop等专业集成电路设计社区,关于自偏置电路的讨论异常活跃。常见议题包括:

- 启动电路(Start-up Circuit)设计:如何确保自偏置电路在加电时能脱离“零电流”简并点,可靠进入正常工作状态。

- 亚阈值区与弱反型区设计:针对超低功耗应用,如何在亚阈值区设计稳定的自偏置电流源。

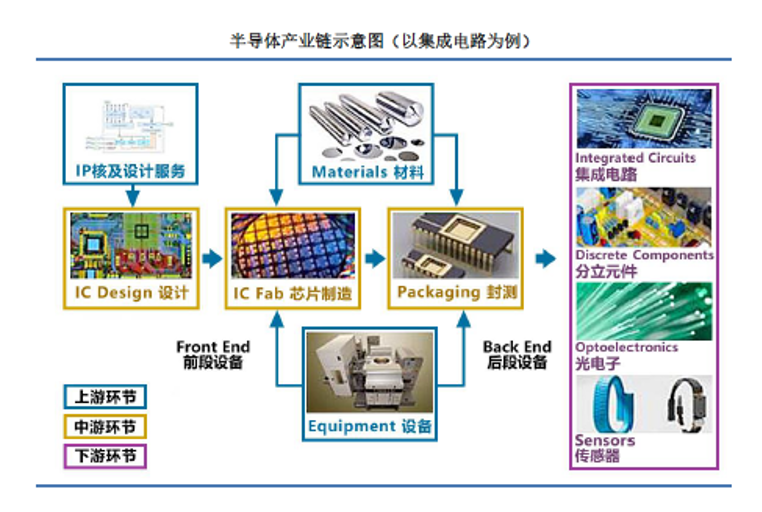

- 先进工艺节点下的挑战:在纳米级CMOS工艺下,短沟道效应、低电源电压对传统自偏置架构的冲击,以及新结构(如亚1V带隙基准)的探索。

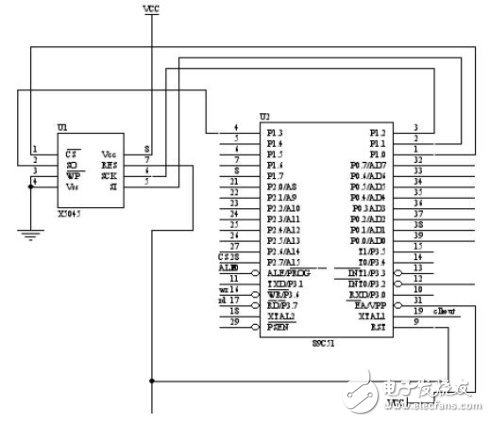

- 与数字辅助技术的结合:如何利用片上的数字电路(如嵌入式微控制器)进行校准和动态调整,实现更智能的自适应偏置,以应对老化(NBTI, HCI)等长期漂移效应。

这些讨论深度结合了集成电路设计的理论知识与工程实践,是初学者入门和资深工程师解决棘手问题的重要知识源泉。

四、与展望

自偏置电路是连接模拟RF IC设计理论与成功流片实践的桥梁。它体现了模拟设计的艺术:在有限的电压余度、工艺变异和噪声预算下,通过巧妙的拓扑结构实现稳定与精准。随着物联网(IoT)、5G/6G通信和汽车电子对高可靠、高集成度射频前端需求的持续增长,对自偏置电路的要求也将越来越高。未来的发展趋势可能包括:与机器学习算法结合进行自动化优化设计、在硅基光电子等新兴领域中的应用,以及面向太赫兹频段的超宽带自偏置技术探索。持续关注EETop等社区的前沿讨论,积极参与分享与交流,将是每一位模拟射频IC设计工程师保持竞争力的关键。